# Intel Trust Domain Extensions (TDX) Security Review

**April, 2023**

Erdem Aktas<sup>1</sup>, Cfir Cohen<sup>1</sup>, Josh Eads<sup>1</sup>, James Forshaw<sup>2</sup>, Felix Wilhelm<sup>2</sup>

```

Executive Summary

Background

Terminology

Intel TDX Threat Model

Design Goals

Adversarial Goals

Leaking TD Secrets

Manipulating TD Behavior

Host Denial-of-Service

Attack Vectors

Malicious Hardware

Malicious BIOS

Malicious SMM

Malicious VMM

Malicious TD/VM

MCHECK

System Validation

Security Concerns

Non Persistent SEAM Loader

Threat Model

Attestation and Rollback Prevention

Security Concerns

Security Vulnerabilities

Unsafe Performance Monitoring VMCS Configuration

Variant Analysis

Remediation

Exit Path Interrupt Hijacking

```

<sup>&</sup>lt;sup>1</sup> Google Cloud Security

<sup>&</sup>lt;sup>2</sup> Google Project Zero

**Exploitation Variant Analysis** Remediation Mitigating controls Persistent SEAM Loader Overview Install initiation TDX module authentication Module installation Page tables "keyhole" mechanism Misconfiguration bugs Mitigating controls **TDX Module Attack Surface** Malicious TDs **Malicious Host Security Review** <u>weggli</u> Frama-C **Discovered Issues** Incorrect loop boundary in tdh sys tdmr init Incorrect error handling in tdh mng rd wr Off-by-one in shared hpa check TLB tracking Address translation Secure EPT **TLB Tracking Algorithm** revert tlb tracking state() vulnerability **Uncore Attack Vector ECC Disablement Vulnerability** MSRs Review Methodology **Attack Vectors TD-to-TDX Module Attacks** VMM-to-TDX Module Attacks Address-Based Attacks Security Concerns VMM-to-TDX Privilege Inversion

Side Channel Attacks and Mitigations

## Speculation based side channel attacks Transient execution attacks **Speculation variants Prediction based** Fault / Assist based Value injection variants Secret output variants Applications to TDX **Mitigations** On hyperthreading Traditional side channel attacks Access oracles Blocked private pages Poisoned cache lines **MONITOR** and **MWAIT** Boosting cache based side channel attacks Zero step / Single step mitigations **Baseboard Management Controller Conclusions** TDX Logical Integrity and Memory Corruption Attacks **Corruption Targets** VMM allocated control structures **SEAM Range** Mitigations **Attestation** <u>Measurements</u> **Debug Security** TD Debugging TDX System Debugging Security Review Results **Future Research Areas Acknowledgments** Google <u>Intel</u>

Appendix A - MSRs of Interest

## **Executive Summary**

This report contains the results of Google's security review into Intel's Trust Domain Extensions (TDX). The Intel TDX feature was added to limited SKUs of the 4th generation Intel Xeon Scalable CPUs<sup>3</sup>. TDX provides hardware isolated virtual machines referred to as Trust Domains (TD), which isolates sensitive resources, such as virtualized physical memory from the hosting environment. This is a valuable addition to the Google Cloud platform as it provides assurances to customers that Google can not access their virtual machine's private information even with full control over the host control mechanisms such as the kernel services and hypervisor.

The primary goal of the security review was to provide assurances that the Intel TDX feature is secure, has no obvious defects and works as expected so that it can be confidently used by both cloud customers and providers. Any defects or weaknesses discovered during the review were fed back to Intel for remediation. A secondary goal was to have a better understanding of the expected threat model for TDX and identify limitations in the design and implementation that would better inform Google's deployment decisions.

The review encompassed source code inspection of the core Intel TDX software components and a review of the design and documentation provided by Intel. Each major area of TDX was reviewed for defects and weaknesses which would impact the security and availability of a deployed virtual machine. Some of the issues inspected were:

- Arbitrary code execution in a privileged security context.

- Cryptographic weaknesses and oracles.

- Temporary and permanent denial of service.

- Weaknesses in debug or deployment facilities.

During the review there was close collaboration between Google and Intel engineers. Questions and issues were handled through a shared issue tracker and regular technical meetings. This allowed Intel to provide deep technical information about the function of the TDX components as well as enabling the reviewers to resolve potential ambiguities in documentation and source code. The review resulted in 81 potential attack vectors and resulted in 10 confirmed security issues and 5 defense in depth changes over a period of 9 months.

This report begins by detailing the Intel TDX threat model as described through a review of the available documentation and discussions with Intel. It then follows with separate sections for each major component of TDX. Each component is described in detail along with what review process was undertaken by the engineers to verify its security properties. Any issues that were discovered during the review are also detailed as well as the status of their mitigations. Intel mitigated the issues discovered before the production release of the 4<sup>th</sup> gen Intel Xeon Scalable processors.

<sup>&</sup>lt;sup>3</sup> TDX is expected to be in general availability in a future Intel Xeon Scalable CPU.

The most serious implementation issue discovered during the review was a bug in the Authenticated Code Module (ACM) responsible for initializing the TDX feature. When the ACM transitions from its privileged execution context back to an untrusted context it incorrectly handles interrupts. The bug allowed untrusted code to execute within the privileged execution mode and compromise the integrity of the TDX feature and the security of any deployed virtual machines.

It was also realized that all ACMs, of which TDX is only one type, can be a weakness in the design as they all run within the same privileged execution context. This means that issues with one ACM could be used to compromise any other. Any ACM that is provided for a platform should be thoroughly reviewed before being used on a production system.

The team identified additional design-level issues during the review process. These issues included the significant number of Machine Specific Registers (MSR) that could interact with the functionality of the TDX. For example, some MSRs could interact with physical addresses assigned to the TDX feature allowing corruption or leaking of sensitive information. Rowhammer was also considered a significant risk to the security of TDX.

All implementation issues were identified in pre-release code. They will all be remediated before the TDX feature officially ships, both for the targeted release on 4<sup>th</sup> gen Intel Xeon Scalable CPUs, as well as the future general release; however, this does mean they will not be assigned a public identifier such as a CVE. Design level issues have been fed back to the Intel engineering team for review internally.

Intel has also opened the source code to the components the team reviewed so that further research can be performed in public. The source includes the TDX Module and Seam Loader SW; however, it omits low-level code such as the microcode used for some of the system's configuration.

Overall, the review has been considered to have met its initial goals of finding and remediating security issues in the implementation and design. There were limits to what was available to review, such as the lack of access to microcode or low-level hardware documentation; therefore, some aspects of the review are based on trust. However, it has also given Google a far greater appreciation of the expected threat model which will be beneficial for subsequent deployment stages.

# Background

In existing virtualization deployments, such as cloud hosting, a virtual machine needs to fully trust the hosting environment and system administrators for the security of any data stored by the machine. While a virtual machine could encrypt data at rest there's little it can do to completely protect the runtime state. The hosting environment has the privilege to inspect and modify the memory and the CPU context to extract secret information while the virtual machine is operational.

Intel Trust Domain Extensions (TDX) is a new architectural component first being introduced in the 4<sup>th</sup> Gen Intel Xeon Scalable CPUs (formerly code-named "Sapphire Rapids") to provide hardware and cryptographic isolation between virtual machines so that less trust needs to be placed in the hosting environment. This includes protecting against a compromised Virtual Machine Monitor (VMM) and boot environment.

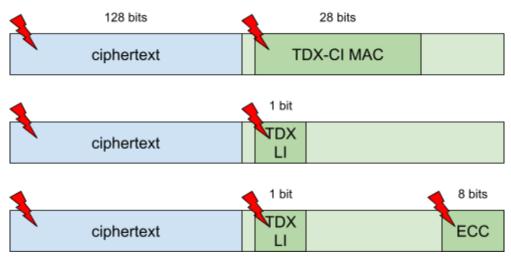

Intel TDX functions by providing a new type of virtual machine guest called a Trust Domain (TD). This guest can only be controlled by a signed Intel TDX module running within a special privilege level, Secure Arbitration Mode (SEAM), which can't be directly accessed by normal code running on the CPU. The memory and context switch state of the virtual CPU is protected using the Total Memory Encryption - Multi-Key (TME-MK) feature built into the memory controller to encrypt data written to physical memory to protect the confidentiality of the TD's state. The integrity of these encrypted contents is additionally protected with either a SHA256-HMAC or a software-inaccessible access control bit.

Intel TDX is of interest to Google Cloud to increase isolation for customer virtual machines and provide a higher level of assurance that Google engineers or systems can't access their data. To be suitable for deployment in customer facing products Google desired additional assurances that the TDX design and implementation met the expected security requirements. For that reason, a team of Google engineers from Cloud and Project Zero were assembled to perform a review of the general design and the software implementation of TDX version 1.0 on Sapphire Rapids (SPR) with full cooperation from Intel.

Security reviews are limited in nature based on the amount of time available and how much access there is to the platform. Based on an initial assessment of publicly available documents it was apparent that TDX is a very complex and dense system, so the team decided to focus only on the areas of most importance.

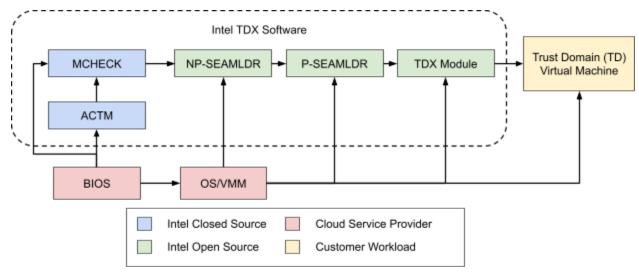

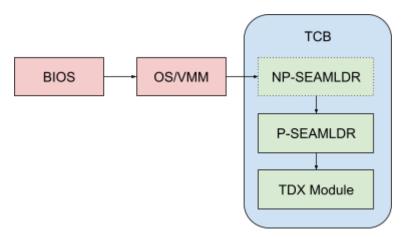

Figure 1: Diagram of Intel TDX Platform Initialization

The diagram above provides an overview of the initialization process for Intel TDX. For the security review we focused on the areas implemented by Intel. Specifically, the following components:

- MCHECK Used by the BIOS to initialize the platform memory configuration

- Non-Persistent SEAM Loader (NP-SEAMLDR)

- Persistent SEAM Loader (P-SEAMLDR)

- TDX Module

These components are all interrelated and a failure of one would have a significant impact on the rest. For example, a flaw in MCHECK has the potential to compromise the entire initialization chain and therefore the security of the encrypted VM.

Anything outside of the four areas, such as the BIOS, Virtual Machine Manager (VMM) and any VM platform support such as Linux kernel changes were not reviewed. The team also did not review the system attestation provided by SGX. Therefore, the scope of the security review encompassed:

- Review of the public and private documentation

- Analysis and review of the source code for the following TDX software components:

- o The TDX module

- The Secure Arbitration Mode (SEAM) loaders to bootstrap the TDX module

- Host VMM to TDX and Guest to TDX APIs

- Provide feedback to Intel of issues discovered and general security improvements

Intel provided the review team with the design documentation and two source code repositories:

- Seam-loader Contains the implementation of NP-SEAMLDR and P-SEAMLDR.

- TDX-module Contains the implementation of the TDX module.

A critical building block in the TCB for TDX is the MCHECK module used to verify a number of system configuration parameters typically set by untrusted elements like the BIOS. At this time the source code for MCHECK is not available for review (and is delivered from Intel encrypted),

which limits the assurances providers and customers can derive from TDX's security properties. The team was also not provided with test systems to perform black-box testing. Additionally, the hardware implementation of the various TDX features was not provided for review. Therefore, analysis of these areas focused around documentation and design review.

This document is a summary of the security review performed by Google including technical details of some issues that were discovered during the process. The source code and specifications for the TDX components have been made open source and are available for download from <a href="Intel">Intel</a>'s TDX web page. This document should provide a useful introduction for further research into the security of the Intel TDX implementation.

# **Terminology**

**Secure Arbitration Mode (SEAM):** A new x86 execution mode designed to isolate the TDX module and SEAMLDRs from entities outside the TDX TCB.

**Non Persistent SEAM Loader (NP-SEAMLDR):** The root-of-trust for Intel TDX. This signed module bootstraps the P-SEAMLDR.

**Persistent SEAM Loader (P-SEAMLDR):** Authenticates and installs (or uninstalls) the TDX module.

**TDX Module:** The software component which manages TDs. The VMM directs it and exposes both guest-facing and VMM-facing APIs.

**Trust Domain (TD):** A VM running under control of the TDX module. Its memory and CPU state are encrypted and integrity protected.

**MCHECK:** Validates the platform has been configured securely before SGX and TDX are initialized. Embedded within the signed and encrypted microcode update blob and run during BIOS.

**Authenticated Code Module (ACM):** Intel's format for signed blobs which are authenticated against a fused key hash and provide a dynamic root of trust.

**Uncore:** All components other than the x86 cores that are still within the Intel SoC. The L3 cache, memory controller, and power control unit are some examples.

**Security Version Number (SVN):** A monotonically increasing number attached to microcode updates, ACMs, and the TDX module. This number is independent from the functional version number and only incremented when security properties change (e.g., vulnerability patch).

**Virtual Machine Monitor (VMM):** The host system used for managing virtual machines, virtual devices, and interacting with external services. In this document and some Intel documents, VMM is used to indicate all host code outside of the TDX TCB once the host OS is running.

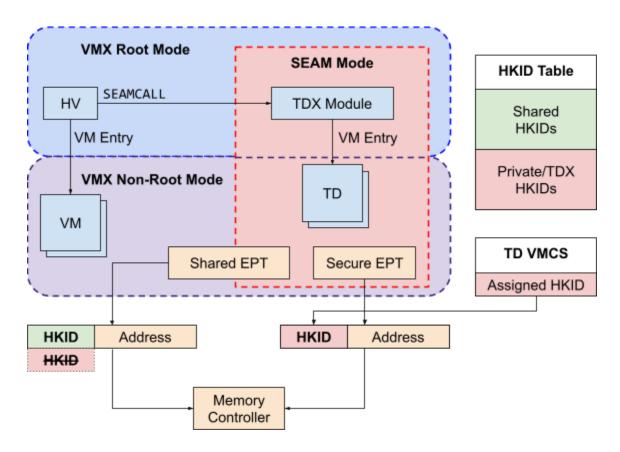

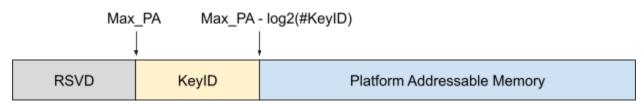

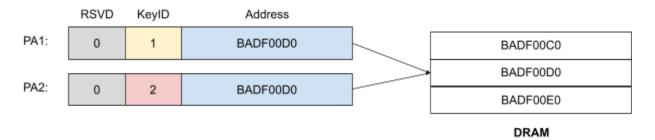

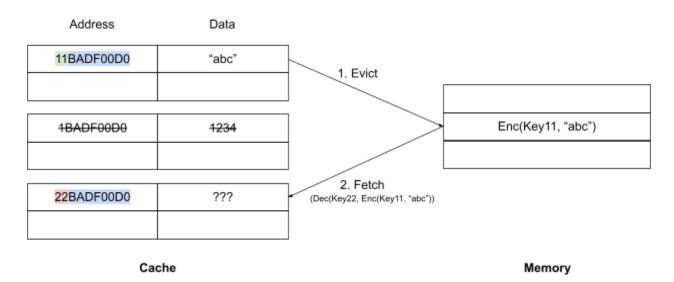

**Intel Total Memory Encryption - Multi-Key (TME- MK):** A feature on recent Intel memory controllers which encrypts DRAM using a key selector stored in the upper bits of the physical address. (Note: TME-MK is sometimes referred in code as "MKTME").

**Host Key ID (HKID):** The TME-MK key selector associated with a given TD. There is only one HKID associated with each TD (and one for the TDX module itself), and they are immutable.

**Poison:** A tracking mechanism within Intel CPUs used to propagate memory errors through the busses until CPU consumption. TDX utilizes memory poisoning to detect and respond to TD memory corruption.

## Intel TDX Threat Model

This section presents our threat model for the Intel TDX technology based on the original design and claims by Intel and our understanding of the various goals an adversary may have when attacking this system. This model informed where we focused our efforts during the review as well as which attacks were out of scope. Intel also published a <u>paper</u> at IEEE SEED in 2021 which describes their threat model and security analysis of TDX.

## **Design Goals**

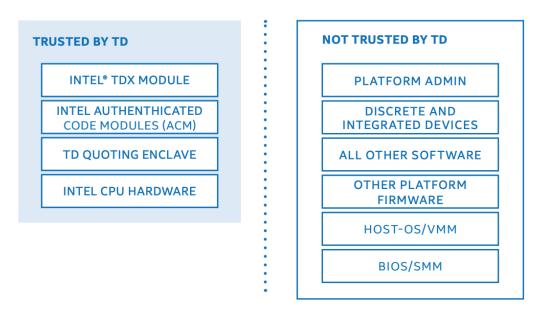

Intel has published a <u>white paper</u> for Intel TDX which provides an overview of the technology, the threats it is designed to mitigate, and the methods for implementation and attestation. TDX asserts a very conservative trusted-computing base (TCB) which only includes the following components:

- Intel TDX module (including P-SEAMLDR)

- Intel Authenticated Code Modules (ACM)

- TD Quoting Enclave (SGX)

- Intel CPU hardware

All other system components are outside of the TCB, including the BIOS, SMM, host OS, and VMM. Additionally, some forms of physical attacks, such as cold-boot and DRAM traffic modification (except for replay), are also outside the TCB and should be protected against. At a high level, only the Intel hardware and signed core firmware should need to be trusted – all other software and design implemented by the cloud service provider can be considered untrusted.

The TDX module handles the bulk of the complex system interactions and is essentially a peer hypervisor interposing between the TD and the host HV/VMM. Writing a bug-free hypervisor is challenging<sup>4</sup> due to the complexities of handling arbitrary guest states and correctly handling complex hardware interactions. Given that bugs in the system are inevitable, a robust attestation system has been incorporated into TDX so that customers can trust their TD is running the latest versions of microcode, firmware, and TDX software.

Overall, this model assumes a sophisticated attacker who potentially has machine ownership/administrative privileges and some physical access – a model many existing technologies were not designed to protect against. Intel TDX is built on a combination of both legacy Intel technologies as well as new hardware and firmware additions.t is important to verify that each of these independently and in conjunction with each other can withstand an attacker who controls so much of the system.

<sup>&</sup>lt;sup>4</sup> See previous vulnerabilities for KVM, Xen, VMware, Hyper-V

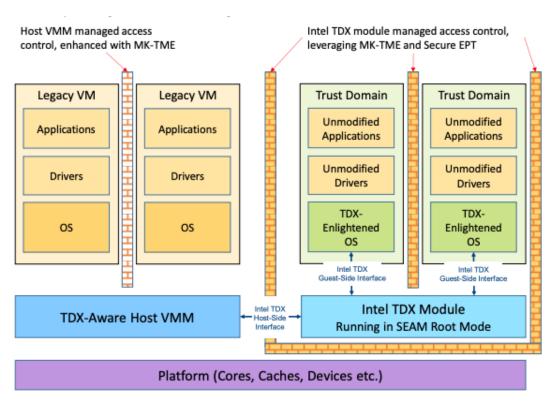

Figure 2: Trust Boundaries for TDX5

#### **Adversarial Goals**

An attacker targeting Intel TDX may focus their efforts on different components depending on what their goals are. In general, an adversary is interested in leaking sensitive information from the TDs, manipulating the behavior of TDs, or using a malicious TD to deny service to the host machine.

## Leaking TD Secrets

After the attestation report is generated and verified, the third-party TD owner is expected to provision secret material to the TD. This information could be in the form of cryptographic keys, intellectual property, private user information, or similar. The goal of TDX's isolation design is to prevent this information from being indirectly or directly leaked to an adversary party.

For example, if there are side channels which exist (e.g., Spectre gadgets in the TDX module, shared resource side channels) then a neighboring TD or the VMM itself may be able to extract partial or complete information from the victim TD. Furthermore, if the TDX module is compromised then an attacker can directly read memory from the victim TD.

## Manipulating TD Behavior

Similarly, an adversary may be interested in modifying the behavior of a victim TD. This could come in the form of direct memory or register corruption which leads to unexpected behavior or execution control. It could also take a more subtle form such as a VMM altering the scheduling pattern of a victim TD or tampering with I/O traffic between the TD and external world.

<sup>&</sup>lt;sup>5</sup> Taken from the <u>Intel TDX White Paper</u>

Additionally, the VMM can modify the memory mapping of the TD (within limits) which may lead to differences in guest behavior.

#### Host Denial-of-Service

Finally, an adversary may simply desire to reduce the availability of a cloud provider by preventing other workloads (TDs, VMs) from being scheduled on a machine. Some of these attacks are more severe than others. For example, there could be a bug where a TD can cause itself to be shut down while another bug in the TDX module may require all TDs on the machine to be immediately halted. Furthermore, some forms of memory corruption and unexpected behavior under TDX can cause an unrecoverable machine check to occur which requires a full power cycle to recover from. Care must be taken in the TDX module to ensure that the risk of these machine checks occurring is minimized in order to prevent widespread availability attacks.

#### Attack Vectors

Due to so few elements on the system being within the TCB for Intel TDX, there are many different attack vectors an adversary can utilize when attempting to degrade the system. Additionally, by combining various attack vectors (e.g., a malicious VMM and TD working together) attackers can reach complex edge cases that the system designers may not have planned for. The sections below list the main pathways an attacker has to interact with the TDX components.

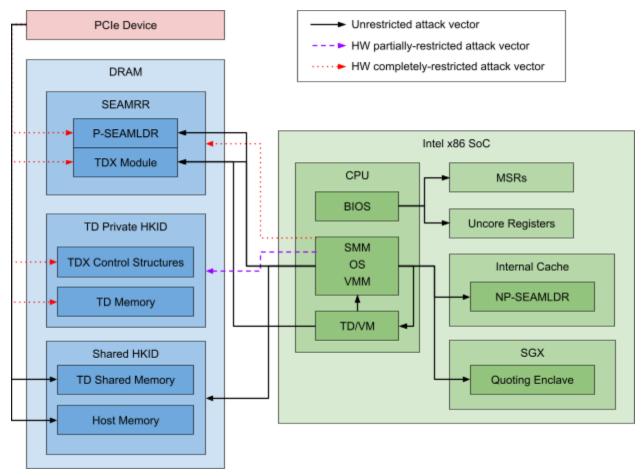

Figure 3: Diagram illustrating the main attack vectors available on Intel TDX. The system is decomposed into external devices (red); external memory (blue); and SoC code, registers, and internal memory (green).

#### Malicious Hardware

Intel states in the <u>TDX whitepaper</u> that TDX 1.0 is designed to withstand some forms of physical attacks such as DRAM capturing and modification; however, there are no protections against physical replay attacks.

PCIe devices such as GPUs and TPUs are sometimes attached directly to VMs in cloud environments. These devices use DMA to directly access the x86 host machine's DRAM and traditionally the host OS is responsible for programming an IOMMU to restrict access and enforce VM isolation. However, when the OS and VMM are outside the TCB, the correct programming of the IOMMU can no longer be relied on. To protect against this attack, PCIe memory TLPs targeting TD private memory (physical addresses with a private HKID set) will be dropped by the IOMMU regardless of host programming. External devices can only interface with TD shared memory which the TD operating system explicitly marks as shared in its guest page tables.

Since physical machines supporting TDX were not available during this review, we left malicious hardware attacks outside the scope of the review.

#### Malicious BIOS

In the Intel TDX threat model, the BIOS (i.e., UEFI) and all code launched by it (OS, VMM) are considered untrusted. This is a significant difference compared to traditional virtualization offerings where no guarantees are made about the trustworthiness of the underlying software. The BIOS is responsible for bringing up all system components and applying the appropriate configuration. Additionally, the BIOS has additional privileges explicitly recognized by the hardware which are significantly restricted when transitioning (by setting the BIOS\_DONE MSR bit) to the operating system. Given this extensive level of system access, ensuring that the integrity of TDX is not compromised by a malicious BIOS is challenging. Intel provides technologies to protect the integrity of BIOS to different degrees (e.g., Bootguard, TXT, PFR). At Google, we use the Titan security chip to ensure that the initial BIOS image that the CPU boots is authentic and produced by Google.

The BIOS has similar access to system configuration as an operating system, but there are additional registers it can access – either due to hardware access controls or lockable registers which will normally be locked by the time the OS gains execution. The BIOS is also responsible for launching MCHECK (responsible for verifying the system has been securely configured) and SGX initialization, both of which are critical for TDX integrity. We enumerated all MSR and Uncore registers accessible by the BIOS, SMM, and OS and attempted to identify any TDX security-relevant registers and bits; however, given the scope of the search space this was not comprehensive<sup>6</sup>. Many of the sensitive registers identified were confirmed with Intel engineers to be checked by MCHECK or had other restrictions which prevented BIOS access from being exploitable.

#### Malicious SMM

The system management mode (SMM) code is responsible for handling a variety of system management tasks and interrupts (SMIs), is more highly privileged than the OS, and is launched by the BIOS. From a threat analysis point of view, if the BIOS is compromised then the SMM module should also be considered compromised. An additional attack vector that can lead to SMM compromise is the SMI handler which services a limited number of requests from the OS. From the hardware point of view, SMM privilege is a mixture somewhere between the BIOS and OS with a few extra bits included (e.g., exclusive access to SMRAM). The main difference for TDX is that SMM persists past the BIOS and is able to attack the TDX module and TDs that are running and potentially attested.

For this review, we did not focus in-depth on SMM but did confirm that many of the access controls that explicitly prevent BIOS and OS access also prevent SMM access. Additionally, we

<sup>&</sup>lt;sup>6</sup> This is an area where future research may be useful to verify there are no gaps.

reviewed the SMM-only MSRs and uncore registers which appear to have effects on TDX security.

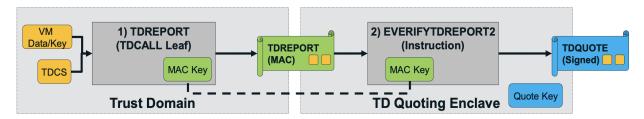

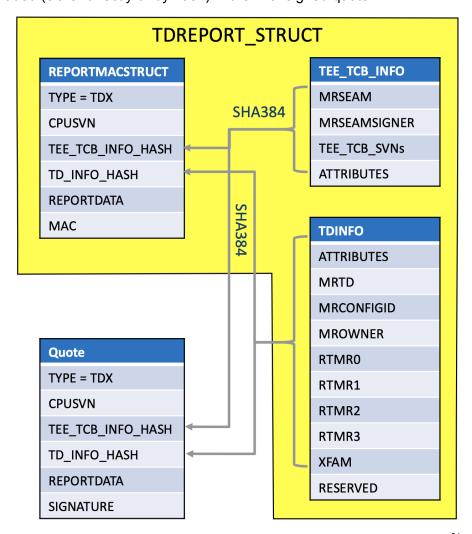

#### Malicious VMM

The host OS, hypervisor and VMM are responsible for kicking off TDX initialization, creating new TDs, and managing the lifecycle of these TDs. The host OS launches NP-SEAMLDR which triggers the measured installation of P-SEAMLDR, later used to trigger the measured installation of the TDX module. Once the system is initialized, the VMM manages the TD lifecycles through the TD Host (TDH) APIs; loading the initial guest image, configuring guest memory, assisting with attestation, scheduling vCPUs, and so on. These responsibilities lead the VMM to have the largest attackable interface into the TDX system. Additionally, the VMM is uniquely responsible for passing information between TDX and the SGX quoting enclave – compromising this chain of trust would remove the legitimacy of attestation.

#### Malicious TD/VM

Finally, the TDs running on the system are guaranteed to be under attacker control and have a unique interface into the TDX system. Legacy VMs do not run under the TDX module, and we did not identify any security concerns regarding their interactions with TDX, but there may be undiscovered issues given their sharing of resources and similar connections to cloud services. The TDs can interact with the TDX module directly through the TDG.\* API calls and VM exit handlers triggered during sensitive operations such as MSR and control register access. Additionally, the TD is a full-fledged virtual machine and can configure the vCPU and memory in any number of unexpected combinations – the TDX module must be able to handle all of these safely.

## **MCHECK**

For technologies where the BIOS is outside the TCB, such as SGX and TDX, the system requires a mechanism to ensure that the BIOS has configured all security sensitive settings to be within an acceptable range. Intel has developed the MCHECK firmware to provide this assurance and deliver the results to TDX in a way that is trusted. MCHECK is implemented as a non-persistent XuCode module and embedded within the CPU microcode update file. It is executed as part of the BIOS boot sequence. The entire microcode update, including the MCHECK XuCode program, is encrypted and signed by Intel. While this provides a trusted way for only Intel to execute microcode updates and MCHECK programs, it also results in a completely opaque security validation which TDX relies upon. Reviewing the MCHECK source code was outside the scope of this security review.

## **System Validation**

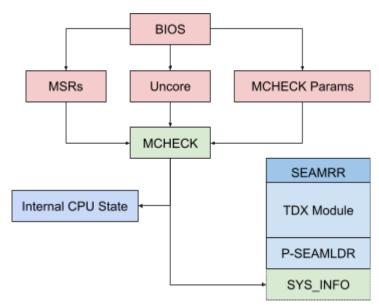

While much of what MCHECK does is not made publicly available by Intel, for TDX there are a few known areas that it must validate before TDX will consider the system in a trusted state. First, MCHECK verifies that the physical DRAM memory has been configured correctly. This includes the absence of address aliasing and checking that security-relevant settings such as refresh timings and ECC are in expected ranges.

Additionally, MCHECK is responsible for verifying that DMA protections are enabled, DDR5 ECC is enabled, memory encryption is configured correctly, and MSR and uncore values are consistently programmed. For TDX, MCHECK derives the HMAC key using RDRAND and later used by the SEAMREPORT for attestation report generation for SGX verification during quote generation.

## **Security Concerns**

MCHECK is an interesting area for security research since TDX (and SGX) rely on it to ensure the BIOS hasn't degraded system security in ways which may open up new exploit pathways. For example, if the BIOS were able to alias two physical memory addresses this would enable bypassing memory access controls such as the SEAMRR region where the TDX module and control structures are located.

Due to the lack of source code and that MCHECK's logic is encrypted, the main security concern we have for MCHECK is its reliance on security through obscurity. There are many edge cases that Intel has confirmed MCHECK validates, but a complete list of what it checks or how exactly these checks are performed is not available. The attack surface of MCHECK is somewhat limited and additionally it can only be executed while in the BIOS execution mode (i.e., before BIOS\_DONE MSR is set). The BIOS populates a somewhat complex data structure that contains a feature bitmap, SGX information, TDX convertible memory ranges (CMRs), and memory topology information. This structure is passed to MCHECK and is the main attack

surface in which one might discover edge cases that are not covered or memory corruption bugs.

Figure 4: Diagram of MCHECK's inputs from the BIOS and output into SEAMRR

Outside of direct attack vectors, we additionally investigated the possibility of the BIOS using software-based fault injection attacks to cause MCHECK to misbehave<sup>7</sup>. There are a couple of design choices that make this attack challenging (MCHECK prevents any other CPU threads from running in parallel, and the OS\_MAILBOX\_INTERFACE from Plundervolt is disabled on Sapphire Rapids), but at least one window remains open. There is an alternative BIOS\_MAILBOX\_INTERFACE for sending commands to the power control unit (PUnit), this includes the ability to send raw SVID commands which result in voltage adjustments. Since there is a delay between when these commands are sent to the voltage regulator and when the voltage actually changes, an attacker might be able to drop the voltage right before executing MCHECK and have the voltage drop hit mid-execution. Evaluating this attack was beyond the scope of this review since we didn't have access to hardware.

MCHECK is Intel-trusted code which runs on the x86 cores and is foundational for ensuring the system has been securely configured before launching SGX or TDX. Outside of limited publications, Intel has provided no public comprehensive details on MCHECK's design and its implementation is a black box (neither plaintext binary nor source available). Based on our discussions with Intel engineers, MCHECK appears to validate and prevent many attacks. Intel also confirmed significant efforts on their part to review and validate this module; however, we could not verify the robustness of these checks ourselves. We strongly encourage Intel to publish the MCHECK source code to enable third party review.

-

<sup>&</sup>lt;sup>7</sup> See <a href="https://plundervolt.com/">https://plundervolt.com/</a> for similar attacks on SGX

## Non Persistent SEAM Loader

Given that the startup BIOS code is outside the TCB for Intel TDX, there needs to be a method for dynamically establishing a root of trust on which the rest of the TDX infrastructure can be loaded. Intel has solved this problem by leveraging the existing Intel TXT and Authenticated Code Module (ACM) technologies to create a new ACM named Non Persistent SEAM Loader (NP-SEAMLDR). In this design, the OS loads NP-SEAMLDR which validates the system configuration, installs the Persistent SEAM Loader (P-SEAMLDR) into the SEAMRR memory region, and returns control to the OS. The OS can then interact with the trusted P-SEAMLDR to install a signed TDX module into the SEAMRR memory region. Finally, the OS interacts with the trusted TDX module to initialize TDX and manage the TD lifecycle.

More details about NP-SEAMLDR and P-SEAMLDR can be found in the <u>SEAMLDR Interface</u> Specification and furthermore Intel has open sourced the code.

Figure 5: Establishment of trust during TDX initialization

An ACM consists of a binary blob of x86 executable code and a header which includes an RSA signature that covers the entire binary except for a scratch section. The Intel SMX GETSEC[ENTERACCS] instruction is used to load and execute an ACM and GETSEC[EXITAC] is used within the ACM to return to the caller. By design, NP-SEAMLDR executes entirely within the internal CPU cache on the primary core (BSP) and requires all other cores on the socket to be idle (i.e., in the wait-for-SIPI state). This reduces the attack surface to preclude system modification while the ACM is running by forcing the CPU into a single-threaded state.

After executing GETSEC [ENTERACCS] and validating the RSA signature, the x86 core switches into 32-bit mode and jumps to the entry point specified in the header. Additionally, the core sets an internal flag which indicates that the processor is now executing in AC mode. One privilege unlocked by entering AC mode is the ability for the CPU to directly access the SEAMRR memory region which is otherwise blocked for BIOS, OS, and SMM execution modes. NP-SEAMLDR requires this access in order to install the P-SEAMLDR binary (which is encapsulated within the NP-SEAMLDR binary) into SEAMRR.

Given that NP-SEAMLDR establishes the trust which the remainder of TDX relies upon, any vulnerabilities here can lead to a cascading compromise of the entire system.

#### **Threat Model**

The overall TDX threat model states that all code outside of the TDX chain of trust is outside the TCB and thus this is the code which can attack NP-SEAMLDR. This includes all ring 0 code on the system; however, NP-SEAMLDR prevents calls from the BIOS progressing beyond the entry code. Additionally, guest VMs and TDs unconditionally trigger a VM exit for all GETSEC instructions and therefore can't attack this interface. This leaves the BIOS (very limited), OS/VMM, and SMM as attack vectors into NP-SEAMLDR.

The interface into NP-SEAMLDR is relatively small, but the attacker has uniquely broad control over the environment in which it runs. There is an explicit <u>ABI</u> which includes 6 general purpose registers to pass arguments which are used either by uCode during load or x86 code within the payload:

- R9: GDT base to be established when returning to the OS

- R10: RIP where control is transferred when returning to the OS

- R11: CR3 value to be established when returning to the OS

- R12: IDTR base value to be established when returning to the OS

- EBX: NP-SEAMLDR ACM physical address base

- ECX: NP-SEAMLDR ACM size

There is also the implicit interface which includes the machine configuration and system register contents. The BIOS has broad privileges to configure all parts of the SoC, including the uncore registers and CPU MSRs. Some of these controls may have effects on the ACM mode transitions and others are parsed by the ACM code itself. Both the implicit and explicit attack surfaces were covered as part of this review.

The NP-SEAMLDR binary protects itself from exploitation in a few different ways. First, the uCode for GETSEC[ENTERACCS] masks all external interrupts such as NMIs and SMIs while also disabling hardware breakpoints. Next, software exceptions are inhibited by setting the IDTR limit to zero which leads to any exception causing a triple fault and system shutdown. Additionally, stack canaries are used but Intel CET control flow integrity and shadow stacks are not used (but are in P-SEAMLDR and the TDX module). Lastly, the binary is loaded at a known virtual address and no ASLR is applied, unlike P-SEAMLDR and the TDX module which have ASLR.

### Attestation and Rollback Prevention

Because NP-SEAMLDR is the root-of-trust for all Intel TDX code, it is critical that customers can verify the system booted their TD using only the latest version of NP-SEAMLDR. If an older, vulnerable version ever loaded it may be possible to corrupt the system's integrity given an

ACM's elevated privileges. Through a combination of hardware registers, SGX, microcode, and NP-SEAMLDR code, the system enforces these properties:

**Attestation:** The end user must be able to cryptographically verify the **lowest**-SVN NP-SEAMLDR that has executed during the boot cycle. This is accomplished through the next two properties.

**Anti-rollback**: For every NP-SEAMLDR executed during a boot cycle, only NP-SEAMLDRs of equal or greater SVN may execute later within the same boot cycle.

**Anti-spoofing:** The recorded SVN for NP-SEAMLDR must never increment.

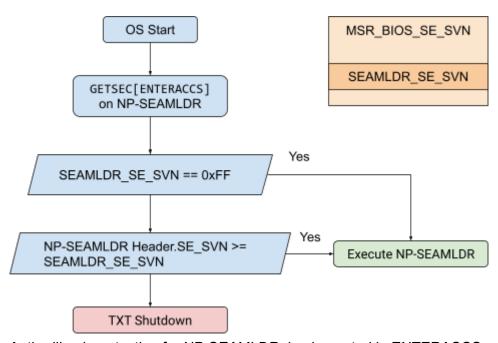

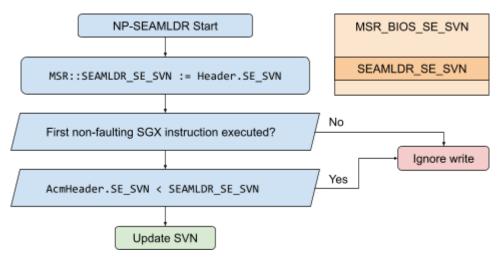

In combination, these properties provide confidence that the SVN recorded (which is used to generate the attestation report and signed quote) indicates the lowest versioned NP-SEAMLDR executed during the current boot cycle. The anti-rollback protection is implemented in the GETSEC[ENTERACCS] microcode which checks the ACM header's SVN against the value stored in BIOS\_SE\_SVN.SEAMLDR\_SE\_SVN – if this value is lower than the previously recorded version a TXT shutdown occurs. On first execution, the SEAMLDR\_SE\_SVN value has not yet been written and execution is allowed.

Figure 6: Anti-rollback protection for NP-SEAMLDR, implemented in ENTERACCS microcode

The anti-spoofing protection prevents a compromised low-SVN NP-SEAMLDR from stating that it was in fact a higher-SVN module which ran. This is implemented in the microcode for WRMSR when writing to the BIOS\_SE\_SVN register and depends on internal SGX state. As soon as the first non-faulting SGX instruction executes on the system, all SVNs in BIOS\_SE\_SVN are locked – this enables SGX to report an accurate minimum security state in attestation. If no SGX

instruction has been executed, then the SVN variables are only allowed to be decremented (and default to 0xFF on reset). SVN's are part of the integrity/authentication controls over Intel issued blobs.

Figure 7: Anti-spoofing protection for NP-SEAMLDR SVN, implemented in WRMSR microcode

## **Security Concerns**

So far, the focus of this section has been on the specific NP-SEAMLDR ACM; however, due to the overall system design, we must also pay attention to all other ACMs which are loadable on the system. Previously, it was mentioned that when the x86 core transitions into AC mode it now has elevated privileges, including the ability to access SEAMRR protected memory. This privilege is not unique to NP-SEAMLDR and in fact applies to all ACMs on the system. This universal application of privileges significantly widens the attack surface for compromising the TDX root of trust. In addition to NP-SEAMLDR, the following ACMs are also known to be loadable on Sapphire Rapids CPUs:

- Alias Checking Trusted Module (ACTM): New ACM for DRAM configuration validation

- BIOS ACM

- BIOS Guard

- SINIT

A vulnerability in any of these ACMs could lead to the same kind of TDX system compromise as previously discussed above. Previous research has discovered <u>multiple vulnerabilities</u> in some of these ACMs. Reviewing each of these modules was outside the scope of this review, but remains an interesting area for future research.

Within NP-SEAMLDR, there are several areas where generic defense-in-depth strategies could add extra hurdles for exploitation. As discussed above, the memory layout of the module is known to the attacker and ASLR of this space (at least for the 64-bit portion) would make attacks more challenging. Similarly, Intel CET features are enabled for P-SEAMLDR and the TDX module but not NP-SEAMLDR. Lastly, the GETSEC[ENTERACCS] instruction disables CR0.WP which enables a memory write primitive to overwrite read-only memory such as the

code itself. After raising this concern with Intel, the NP-SEAMLDR code was updated to enable CR0.WP during the 32-to-64-bit transition.

## Security Vulnerabilities

While reviewing NP-SEAMLDR, we discovered a variety of vulnerabilities in the pre-release code, some of which are described below. Each of these vulnerabilities have been fixed and verified in the current release.

#### Unsafe Performance Monitoring VMCS Configuration

By design, the core performance monitors should be disabled while executing in P-SEAMLDR or the TDX module. TD guests should also have these features disabled unless the guest is created with the attestable ATTRIBUTES.PERFMON = 1 or ATTRIBUTES.DEBUG = 1 values set. The reason for this is twofold: first, to prevent information leakage of TDX and TD secrets to the host; and second, to prevent host control over performance features which write records during TDX execution.

These performance monitoring controls are configured by writing to CPU MSRs such as IA32\_PERF\_GLOBAL\_CTRL. In order to prevent these configurations from persisting from host execution into TDX or TD execution, there are VMCS entry and exit controls which direct the CPU to context switch on transition.

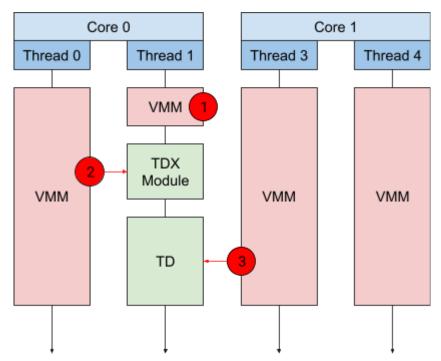

For the TDs, the TDX module is in charge of configuring the VMCS and will set the entry/exit controls based on the ATTRIBUTE bits described above. For the TDX module, a similar method is used where the transfer VMCS (taken from the <a href="STM design">STM design</a>) is configured such that IA32\_PERF\_GLOBAL\_CTRL is always context switched. There is one transfer VMCS per physical CPU, each of which are located within the TDX module and configured by P-SEAMLDR during the install command. P-SEAMLDR follows a similar design to the TDX module, but instead has a single transfer VMCS which is installed by NP-SEAMLDR.

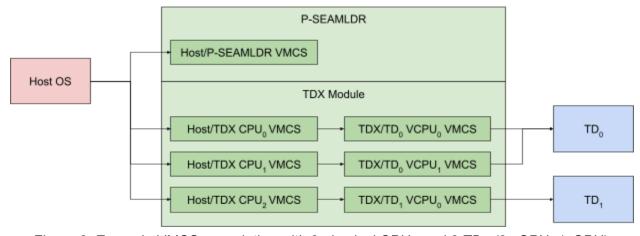

Figure 8: Example VMCS association with 3 physical CPUs and 2 TDs (2 vCPU, 1vCPU)

While reviewing how performance monitors are context switched as described above, a discrepancy was discovered between the P-SEAMLDR transfer VMCS and TDX module transfer VMCS. In P-SEAMLDR, the VM-exit control<sup>8</sup> for saving IA32\_PERF\_GLOBAL\_CTRL was set but the similar control for *loading* the MSR was cleared. This results in the host MSR value persisting into P-SEAMLDR's execution. The resulting effect is that core performance counters continue incrementing while P-SEAMLDR is executing and if any of them rollover then a performance monitoring interrupt (PMI) will occur. P-SEAMLDR doesn't contain any secret material, so using the performance monitors to leak information was not relevant. However, the system can be configured such that a PMI triggers the CPU to write information about the event into memory at a user-specified address. For example, the Processor Event-Based Sampling (PEBS) feature can be programmed via the IA32\_DS\_AREA MSR to write such data on a PMI. The result is that a malicious host OS can configure the PMUs and PEBS such that a PMI occurs during P-SEAMLDR execution which then writes semi-controlled data into an arbitrary address. Given that P-SEAMLDR is responsible for authenticating and loading the TDX module, this vulnerability could lead to a full TDX compromise.

#### Variant Analysis

To proactively discover similar issues where the P-SEAMLDR and TDX transfer VMCS differ, Intel dumped both of these structures in a test environment and searched for any unexpected differences. Additionally, the VMCS configuration code was reviewed with a focus on finding similar edge cases where performance monitors could be enabled.

#### Remediation

We did not attempt to exploit this vulnerability due to the fact that an ASLR defeat would also be required to determine the base of P-SEAMLDR. Since NP-SEAMLDR is responsible for initializing the transfer VMCS for P-SEAMLDR, the bug is in NP-SEAMLDR but only affects P-SEAMLDR. This issue was fixed by configuring the VMCS to load the IA32\_PERF\_GLOBAL\_CTRL MSR on VM exit (VMM to P-SEAMLDR transition).

## Exit Path Interrupt Hijacking

Previous <u>research</u> has highlighted the importance of ensuring that trusted-to-untrusted domain transitions are complete and well understood by both sides. For TDX, the transitions into NP-SEAMLDR, P-SEAMLDR, and the TDX module must be complete and not implicitly trust any attacker-controlled data that may be present in system registers. Similarly, the transition back to the VMM or TD must ensure that the context switch is complete and no sensitive TDX state remains in system registers. This section describes a vulnerability that was discovered in the NP-SEAMLDR where attacker-controlled content was implicitly trusted during a short window during the exit transition.

<sup>8</sup> For the P-SEAMLDR and TDX module transfer VMCS, the transition from host OS to P-SEAMLDR/TDX is considered a VM-exit while the transition back is considered a VM-entry.

As mentioned in the overview of NP-SEAMLDR above, the ACM code masks all external interrupts and translates software exceptions into a system shutdown. External interrupts are masked throughout ACM execution due to configuration registers which are set by the GETSEC[ENTERACCS] microcode on entry. For software exceptions however, the ACM entrypoint x86 code disables interrupts by quickly reconfiguring the interrupt descriptor table (IDT) to point to a null descriptor. This effectively makes any software fault (e.g., page fault, general protection, ...) cause the hardware to fault again when performing the interrupt lookup, leading to a triple fault which finally leads to system shutdown. Conversely, on the ACM exit path the original IDT descriptor is restored before returning to the host via the GETSEC[EXITAC] instruction.

```

AcmEntryPoint PROC NEAR

nop

nop

nop

; Right after ENTERACCS, SEAMLDR 32-bit assembly code will do the following:

; SIDT saved OS IDTR

; LIDT null IDTR // a 48-bit variable that contains 0's

sidt

fword ptr ds:[ebp + stackStart + 4*6]

; Make sure that Null IDTR is actually zero

dword ptr ds:[ebp + stackStart + 4], 0

mov

dword ptr ds:[ebp + stackStart + 4 + 4], 0

mov

lidt

fword ptr ds:[ebp + stackStart + 4]

; Load NULL IDTR

```

32-bit entry code for NP-SEAMLDR

```

lidt FWORD PTR [rcx].SEAMLDR_COM64_DATA.NewIDTR ; Load attacker IDTR

lgdt FWORD PTR [rcx].SEAMLDR_COM64_DATA.OriginalGdtr

;; <truncated for report>

DoExitAC:

;; Parameters for EXITAC

; uCode restores the RIP from RBX during EXITAC

mov    rbx, QWORD PTR [rcx].SEAMLDR_COM64_DATA.ResumeRip

; uCode restores the CR3 from R8 during EXITAC

mov    r8, QWORD PTR [rcx].SEAMLDR_COM64_DATA.OriginalCR3

; SEAMLDR Error code is reported in R9

mov    r9, QWORD PTR [rcx].SEAMLDR_COM64_DATA.RetVal

; Clear all flags

```

```

mov rdx, 0

; Do ExitAC

mov rax, EXITAC

push 2

popfq

;; Clear other registers as described in spec - not xor to avoid changing flags

mov rcx, 0

;; <truncated for report>

GETSEC[EXITAC] ; drop privileges and return to host x86 code

```

#### 64-bit exit code for NP-SEAMLDR

From an attacker's perspective, this presents an interesting window: there is a point of time shortly after ACM entry and shortly before ACM exit where the host's IDT is still configured. If an exception can be forced to occur within these windows the attacker can gain control over RIP while in privileged AC mode.

On the entry path, the attacker has no influence over the instruction operand values or the EBP base register (this points to the base of the ACM) which is dereferenced while the attacker's IDT is still active. However, on the exit path, the code restores the host state before executing GETSEC[EXITAC] which completes the transition back to regular x86 mode. In this path, we noticed that if a non-canonical GDT base address is passed to the ACM then the context switch which executes LGDT will raise a #GP exception. At this point, we wrote a quick proof of concept to demonstrate control of RIP while still in AC mode.

#### Exploitation

While the attacker does have control of IDTR, there are some environmental restrictions that must be overcome. Critically, the ACM only has its own module image mapped into memory after transitioning to 64-bit mode which means an attacker can't place their malicious IDT outside of the ACM image or it will #PF and triple fault. Since the ACM image is signed and verified, this means that an attacker also can't modify the signed image to inject an IDT.

Luckily for the attacker, there is a portion of the ACM image which is unsigned – the scratch space. For NP-SEAMLDR, this space is 832 bytes long which is plenty of room for the required IDTR and IDT descriptor. In <u>Simics</u><sup>9</sup>, this scratch space is still accessible in ACRAM and still contains the modified values; however, on real hardware a subset of this space is used for RSA calculations.

<sup>&</sup>lt;sup>9</sup> Due to hardware access limitations during this early technology review, we relied on the Simics simulation environment for dynamic testing.

A proof of concept was created as a UEFI application that runs from the UEFI shell in Simics with the SPR module installed.

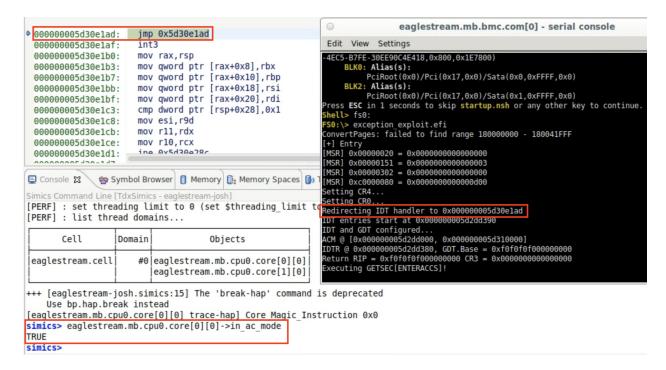

Figure 9: Demonstration in simulation of RIP control while in privileged AC mode

#### Variant Analysis

After this vulnerability was discovered, we continued to look for any other method for causing an exception during these execution windows. One additional variant was discovered in the final instruction which executes, GETSEC[EXITAC]. This is a complex, microcoded instruction that implements the context switch from AC mode back to regular x86 mode. Looking through the Intel specification for the operations performed by this instruction show several opportunities for causing an exception, although most are not possible given the constraints.

However, one condition is possible to reach given the original code. The NP-SEAMLDR ACM needs to know where to return execution to on exit and in this design, the host OS originally passes the return address during GETSEC[ENTERACCS] via the R10 register. Similar to the original issue, an attacker can specify a non-canonical value for R10 which will cause a #GP exception to occur on execution of GETSEC[EXITAC]. Critically, this exception occurs **before** the transition out of AC mode, so the attacker retains this privilege.

```

ELSIF (

(in VMX operation) or ( (in 64-bit mode) and ( RBX is non-canonical ) )

(CR0.PE=0) or (CPL>0) or (EFLAGS.VM=1) or

(ACMODEFLAG=0) or (IN_SMM=1)) or (EDX ≠ 0))

THEN

```

```

#GP(0);

... // segment cut for brevity

ACMODEFLAG := 0;

```

#### Portion of GETSEC[EXITAC] operation listing

Other ACMs have a similar return path where caller state is restored before executing GETSEC[EXITAC]. As far as we know, all these ACMs run in 32-bit mode so the specific issue concerning non-canonical addresses is not applicable; however, there may be alternative ways to trigger an exception after IDTR has been loaded<sup>10</sup>. We tested many theories locally using Simics and worked with Intel engineers to test some of these experiments on SPR hardware. Compromise of any ACM leads to execution in a highly privileged mode which can impact TDX and platform security.

#### Remediation

Intel fixed both variants of this vulnerability in the 1.0 release. The original exception path during LGDT was fixed by moving the LIDT instruction directly before the register clearing and GETSEC[EXITAC] instruction. The non-canonical return address exception path was mitigated during entry by verifying the requested return address is actually canonical.

While the vulnerability is fixed in the latest signed version of NP-SEAMLDR, there must also be mechanisms in place to prevent (or detect) the older vulnerable versions from being loaded. There is no persistent revocation list for TDX, so older versions of NP-SEAMLDR can always be loaded on supported hardware; however, the version loaded is securely stored and later used during attestation<sup>11</sup>. To get around this attestation artifact, an attacker might try first loading a low-version vulnerable NP-SEAMLDR, then compromising the TDX boot chain, and finally loading a high-version NP-SEAMLDR before attestation occurs. This technique is thwarted by the anti-spoofing mechanism described in the <u>previous section</u>. Therefore, a TDX customer can trust that only a specific range of NP-SEAMLDR modules were loaded before provisioning secrets to their TD.

## Mitigating controls

The NP-SEAMLDR has a set of defensive measures that make exploitation harder. This includes the following:

Constrained execution model: The GETSEC[ENTERACCS] instruction used to launch NP-SEAMLDR requires all logical processors in the socket be in the WAIT-FOR-SIPI

<sup>&</sup>lt;sup>10</sup> For example, 32-bit ACMs can #GP on GETSEC[EXITAC] if the return address is above the CS limit. However, in these ACMs the return address is not arbitrary and instead is set to the address of the instruction following GETSEC[ENTERACCS].

<sup>&</sup>lt;sup>11</sup> Included as CPUSVN by the SEAMOPS[SEAMREPORT] instruction executed from the TDX module.

- state (not able to execute instructions). Additionally, external interrupts and debug features like hardware breakpoints are disabled during NP-SEAMLDR execution.

- Fail-closed: Exceptions cause a triple fault and a machine shutdown.

- **Heap**: No dynamic heap allocations prevent the risks commonly associated with bad object management, such as use-after-frees.

- Extremely small attack surface: There is almost no user input to NP-SEAMLDR, mostly just CPU state to restore on the exit path. Additionally, this input is only given on entry with no post-launch command handling.

- Secrets: NP-SEAMLDR, by design, does not hold or process any secret key material.

## Persistent SEAM Loader

## Overview

The persistent SEAM loader, or P-SEAMLDR, is responsible for **authenticating**, **loading** and **measuring** the TDX module. It is embedded in the NP-SEAMLDR binary and is loaded dynamically to the top of SEAM range by the NP-SEAMLDR ACM.

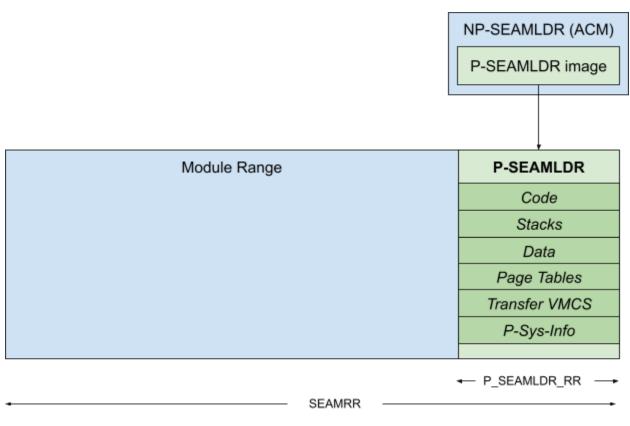

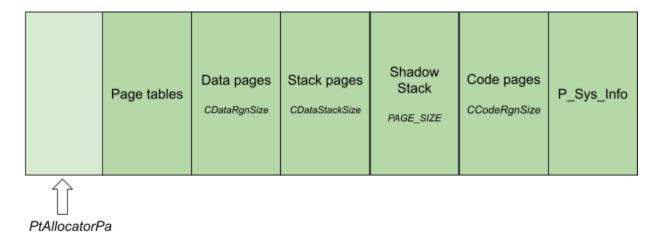

NP-SEAMLDR sets up the environment for the P-SEAMLDR: copies code and data pages, initializes stack pages, configures page tables that translate linear addresses to physical addresses, and configures the VMCS required to enter SEAM root-mode (figure 10).

Figure 10: SEAM setup after NP-SEAMLDR

SEAM state is captured in a special platform-scope register (only accessible by uCode or SEAM code) called CR SEAMEXTEND. It includes the following fields:

| P-SEAMLDR Ready       | Flag indicating P-SEAMLDR is loaded successfully in SEAM range. CPU uCode checks this flag before entering SEAM root-mode on a SEAMCALL instruction.       |

|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P-SEAMLDR Mutex       | Lock for entering P-SEAMLDR. Acquired on SEAMCALL, released on SEAMRET. CPU enters P-SEAMLDR only when this lock is clear.                                 |

| SEAM SVN, Late SE SVN | "Security Version Numbers" captured during load. These are included in the attestation report.                                                             |

| SEAM Ready            | Flag indicating TDX module is loaded successfully in SEAM range. CPU uCode checks this flag before entering SEAM root-mode on a SEAMCALL instruction.      |

| SEAM Under Debug      | Flag indicating system is under debug. A system under debug does NOT produce valid attestations as SGX signing enclave is loaded with non-production keys. |

Note how the P-SEAMLDR mutex forces a single-threaded execution model for the loader.

The loader exposes a set of APIs to install and shutdown the main TDX module. The shutdown operation also clears the "P-SEAMLDR ready" flag in CR\_SEAMEXTEND, thus allowing P-SEAMLDR reinstallations and upgrades.

#### Install initiation

The installation process is designed to run serially on all logical processors (LPs), where the work is done on the last LP that invoked P-SEAMLDR's install API.

A two-step process is designed to ensure that no other LPs are running in SEAM mode while a module installation is in process: 1) The loader clears the "SEAM Ready" flag in CR\_SEAMEXTEND. This blocks LPs from entering SEAM mode. 2) The loader tracks which LPs have called the Install API. Installation starts only when the bitmap is full, meaning all LPs have called P-SEAMLDR. Note that P-SEAMLDR cannot race with itself (P-SEAMLDR Mutex), and once an LP calls P-SEAMLDR it cannot SEAMCALL into a previously loaded TDX module (SEAM Ready is cleared).

#### TDX module authentication

The P-SEAMLDR accepts a seamldr\_params argument that points to the TDX module binary in physical memory, and a seam\_sigstruct parameter, also called a manifest, that authenticates the TDX module binary.

#### Authentication is as follows:

- Loader authenticates the RSA verification key: SHA-384 of SIGSTRUCT.MODULUS is equal to a hard coded constant, INTEL\_SIGNER\_KEY\_HASH, embedded in P-SEAMLDR.

- Loader authenticates the manifest: manifest fields have the correct signature under the RSA-3072 modulus key. Signature scheme is EMSA-PKCS1-v1.5 with SHA-384 message digest.

- 3. Loader authenticates the **module**: module's SHA-384 digest matches the expected digest listed in the manifest.

The chain of trust from the NP-SEAMLDR to the dynamically loaded TDX module is preserved.

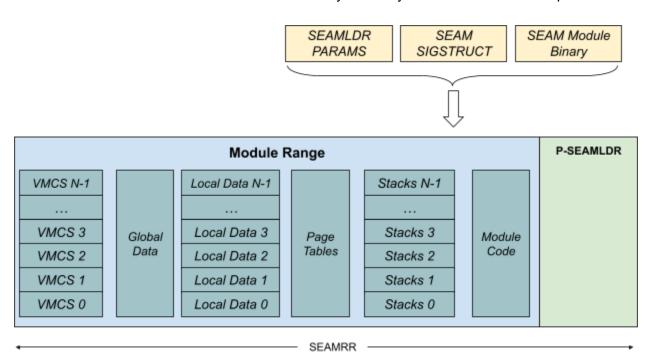

Figure 11: SEAM setup after P-SEAMLDR

We reviewed the authentication scheme for correctness and security: we confirmed the signing key is used for a single purpose, message parsing is unambiguous, and only strong, well-known primitives are being used. Sigstruct and module binary are copied from host memory to private SEAM range before being authenticated, so there's no risk of TOCTOU. Length values are sanity checked.

Finally, we tested the implementation - Intel Integrated Performance Primitives Cryptography library, or <a href="IPP">IPP</a> - using <a href="Wycheproof">Wycheproof</a> test vectors. We confirmed the library correctly handles edge cases in the RSA verification code, and doesn't have implementation issues parsing the DER encoded digest.

#### Module installation

Similar to how the NP-SEAMLDR sets up the execution environment for the P-SEAMLDR, the latter does the same for the TDX module. The loader copies the module's code and data pages to SEAM range, prepares local data and stack regions for each of the N logical processors, prepares the N transfer VMCS, and configures the page tables. On successful installation, the loader stores the module's measurement (*sigstruct.seamhash*) in CR\_SEAMEXTEND, and sets the "SEAM Ready" flag to True.

## Page tables "keyhole" mechanism

The P-SEAMLDR constructs page tables that are, for the most part, **static**. The page tables map linear addresses to physical addresses such that when the module runs in 64b protected-mode, it has access to its own code and data pages. Since the mappings are static, the page tables are global, and can be safely used concurrently by different LPs.

There are flows in the module that require **dynamic** mappings. For instance, when the module reads input arguments from host physical addresses, it first needs to map it to its virtual address space. In order to support dynamic mappings, the loader reserves a region - a page table directory - for this purpose. This region, also called a "keyhole", is mapped with RW permissions to the module's address space. At runtime, the module constructs page table entries (PTE) in the keyhole page, and uses the appropriate linear address to access outside host memory. Each LP gets a dedicated keyhole space for its own dynamic mappings. This prevents race conditions between LPs.

A similar mechanism exists for the P-SEAMLDR. The NP-SEAMLDR constructs static page tables with a RW keyhole for P-SEAMLDR dynamic mappings.

We thoroughly reviewed the page table configuration and TLB management in both the loader and the TDX module. We verified they properly manage the TLB during dynamic mappings: the TLB is flushed using INVLPG if a cached entry is being reused. We identified that a crucial piece of TLB management - TLB shootdown - is missing in the code. However, we confirmed with Intel engineers that this is safe. Each logical processor has dedicated keyholes with a distinct set of linear addresses, so TLB and other paging structure caches are always coherent across the LPs, and there's no need for a shootdown.

## Misconfiguration bugs

We identified an implementation bug in how the NP-SEAMLDR constructed the P-SEAMLDR page tables. The P-SEAMLDR layout is as follows:

Figure 12: P-SEAMLDR layout

An internal *MapPage()* adds new static mappings and "grows" the page table to the right. It tracks the current page table size using the *PtAllocatorPa* variable. On entry, the function performs a sanity check that there's sufficient space remaining to add the new mapping. The check verifies the updated PtAllocatorPa does not overlap with the data region:

Notice that the shadow stack size is not accounted for, and <code>MapPage()</code> computes an incorrect offset for the data region. If <code>PtAllocatorPa</code> crosses over the data region, <code>MapPage</code> builds valid page table entries that overlap with data variables. In an extreme case, P-SEAMLDR operations could overwrite valid PTEs, and potentially point them to attacker controlled data. This was fixed by adding the shadow stack size to the expression.

A second finding was in how P-SEAMLDR translated virtual addresses (VA) to physical addresses (PA) by subtracting the data region base address:

```

uint64_t offset_in_data_region = va - st_p->data_rgn_base;

// Set by NP-SEAMLDR to C_DATA_RGN_BASE | SeamldrData.AslrRand (0xFFFF800300000000)

```

This computation is correct for VA pointing at variables in the data region. However, there were flows that passed pointers to the stack region, for instance *seamldr info()*:

```

ALIGN(256) seamextend_t seamextend;

...

seamextend_read(&seamextend);

```

This computation va - st\_p->data\_rgn\_base "blows up", since the stack's base address is set to C\_STACK\_RGN\_BASE (0xFFF800100000000), a much smaller value than C\_DATA\_RGN\_BASE (0xFFF800300000000). The fix uses a temporary buffer on the stack.

## Mitigating controls

The P-SEAMLDR has a set of defensive measures that make exploitation harder. This includes the following:

- **Constrained execution model**: P-SEAMLDR mutex guarantees a single threaded execution model the loader cannot race with itself. Furthermore, interrupts and NMIs are inhibited, so unexpected code paths are not allowed during P-SEAMLDR operation.

- Fail-closed: exceptions cause a triple fault and a machine shutdown.

- State: bitmap tracking logical processors guarantees installation sessions are serialized.

- **Heap**: no dynamic heap allocations prevent the risks commonly associated with bad object management, such as use-after-frees.

- **Input validation**: loader performs extensive input validation. Furthermore, data is copied from host memory to SEAM range before being validated.

- ASLR: NP-SEAMLDR randomizes the base virtual address for code and data regions of the P-SEAMLDR.

- **CET**: control-flow enforcement is enabled. This feature uses shadow stacks and indirect branch tracking, and blocks return/jump-oriented programming attacks.

- Mappings: most page table mappings are static. Dynamic mappings go through per-LP keyholes. TLB is flushed on SEAM transitions, and on new mappings. Entries are marked as user-owned which in combination with SMAP prevents an arbitrary write from modifying these keyhole mappings.

- Secrets: P-SEAMLDR, by design, does not hold or process any secret key material.

- **Side channels**: P-SEAMLDR enables mitigations against speculation based side channel attacks.

- Host MSRs: transfer VMCS masks MSRs that are controlled by the host VMM.

## **TDX Module**

The Intel TDX module is the central privileged software component for running confidential VMs (called TDs). P-SEAMLDR installs the module into the protected SEAMRR memory range and runs in SEAM Root Mode giving it full access to the host OS and all TDs. It is responsible for creating and managing Trust Domains and enabling communication between the host VMM and TDs, while enforcing access controls. A <u>detailed specification</u> and source code are publicly available.

Figure 2.1: Intel® Trust Domain Extension Components Overview

Figure 13: TDX Components

The TDX module provides host-side and guest-Side APIs. The host calls into the TDX module by using the SEAMCALL instruction, the TD triggers its API using TDCALL.

The host-side interface can be used to initialize and manage the TDX module state, configure TDs and manage their private memory regions.

The guest-side interface is smaller and offers functionality for runtime attestation and measurement, and a hypercall mechanism to enable TD->VMM communication.

A core responsibility of the TDX module is physical memory management. Both TDX internal control structures and TD private memory are stored in physical memory ranges which are configured by the host VMM. This is done by configuring so-called Trust Domain Memory Region (TDMRs) which describe the physical memory space usable by TDX. Internally, the TDX module manages metadata for all used memory pages in a data structure called Physical

Address Metadata Table (PAMT). PAMT entries describe the owner and type of each physical page and are also used as part of <u>TLB tracking</u>.

#### **Attack Surface**

All code outside of the TDX chain of trust can be a threat to the TDX module. At a high level we can differentiate between attackers that have some level of control over the host (e.g. malicious administrators or a compromised BIOS) and attackers that only control one or more guests.

#### Malicious TDs

The TDX-specific attack surface reachable by a malicious TD is small but important. A malicious guest should not be able to negatively influence the hosts or other guests. The main attack surface in the TDX module is the handling of VM exits and TD calls as implemented in the src/td dispatcher directory.

#### Malicious Host

TDX needs to defend against malicious or compromised hosts. While all components outside of TDX are untrusted, it still makes sense to distinguish between attacks that only require OS/VMM control, attacks that additionally require a SMM compromise and attacks involving the BIOS. A Cloud Service Provider that wants to use TDX to protect against malicious OS administrators, would not consider attacks requiring a compromised BIOS critical as long as BIOS integrity can be verified.

The largest attack surface of the TDX module is the SEAMCALL API interface implemented in the src/vmm\_dispatcher directory. In addition, several system wide components can be configured and manipulated by a malicious VMM, BIOS or SMM to indirectly impact the secure operation of the module (see the MSR and uncore sections).

Naturally, a malicious VMM can spin up an arbitrary number of cooperating malicious TDs so issues that involve attacks from both sides of the virtualization stack need to be considered as well.

## Security Review

As the TDX module is a large and low level C codebase, much of our review concentrated on typical C language issues like temporal and spatial memory safety, integer truncation or overflows, concurrency issues and correct error handling.

In addition, we looked for application specific issues that could break TDX's security invariants. These include:

Access to VMM controlled pointers. The TDX module needs to ensure that these point to VMM-owned or shared memory.

- Validation of TD VMCS state. Depending on the TD configuration (debug vs. non-debug), the VMM has limited control over parts of the TD VMCS configuration. The TDX module needs to ensure that all VMM controlled VMCS fields are sanitized. For example, VMM controlled physical pointers in the VMCS need to point into shared memory and be correctly aligned.

- Physical Memory invariants. The TDX module uses physical memory pages offered by the VMM to store both TD guest data, internal metadata and the secure EPTs of all TDs. Special care must be taken to ensure that a single physical page is always used in a single context and no "type confusions" occur. Pages that are reused in other contexts need to be correctly reinitialized. Finally, TLB tracking needs to ensure that no stale mappings are left over in the TLB.

While we did discover some issues during the review, we were impressed with the overall quality of the codebase. The APIs exposed to the VMM and TD are small, well-designed and don't rely on overly complex input or output parameters. Security critical functionality like access to physical addresses is done using helper functions that implement all the necessary checks and locking in a single place.

While manual code review is often required to find security issues in complex code bases, fuzzing and static code analysis can be used for better coverage. In this case, fuzzing was not possible as we did not have access to suitable test systems. However we used two static analysis tools to assist with our review:

#### weggli

<u>weggli</u> is a code search tool for C and C++ codebases designed to help security researchers identify interesting code patterns. We used weggli to assist our manual review by running both generic and target specific queries over the codebase. Examples are shown below:

Find functions that use an argument as dynamic array index:

```

_ $func(_ $index) {_[$index];}

```

Find functions where the return value isn't always checked:

```

_ = $func(_);' -p 'strict: $func(_);

```

Search for suspicious early returns (this query identified a bug in the TDX module):

```

_ $func(_) {

goto $LABEL;

return _;

```

```

goto $LABEL;

}

```

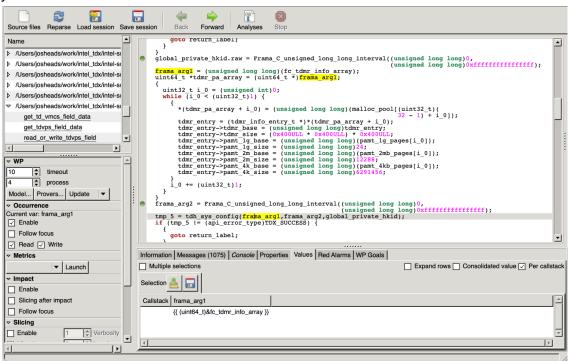

#### Frama-C

<u>Frama-C</u> is a static analysis framework for C/C++ codebases. Through a combination of the E-ACSL, evolved value analysis, and weakest precondition plugins, Frama-C analyzes a target codebase while tracking variable value sets and attempting to prove the absence of C/C++ undefined behavior. Since we were unable to dynamically run the SEAMLDR or TDX module code, static analysis was an attractive option to attempt to find bugs missed through manual analysis.

Figure 14: Screenshot of Frama-C analysis before TDH.SYS.CONFIG API call

We wrote scaffolding to simulate the TDX module simulation and then analyze the host-facing API calls with user input annotated as attacker controlled. There was limited success in running this analysis due to the nature of the TDX module and time constraints. Many of the TDX module APIs with user input deal with memory management and directly access raw pointers into memory outside the scope of the TDX module. This activity would normally indicate a bug in a program, so we had to model these memory accesses in various ways to eliminate false positives. A majority of the APIs were analyzed using this method with no true positives, but more effort is necessary to be fully confident in the results.

Given the relatively small size of the SEAMLDR and TDX module code, formal verification of part or all of these components may be worthwhile.

#### Discovered Issues

Incorrect loop boundary in tdh\_sys\_tdmr\_init

The TDH.SYS.TDMR.INIT handler function tdh\_sys\_tdmr\_init defined in src/vmm\_dispatcher/api\_calls/tdh\_sys\_tdmr\_init.c is used to initialize parts of the Physical Address Metatable (PAMT) of a Trust Domain Memory Range (TDMR).

When tdh\_sys\_tdmr\_init is called with a physical address as its argument, it needs to make sure that the address is actually part of a configured TDMR. It does so by iterating through the tdx global data ptr->tdmr table as shown below:

Crucially, this code assumes that all array indexes smaller than MAX\_TDMRs are configured correctly. However, if we look at thd\_sys\_config,the function responsible for initializing the table, we can see that callers can choose an arbitrary number of TDMRs to initialize as long as it's smaller or equal to MAX\_TDMR:

```

num_of_tdmr_entries);

retval = api_error_with_operand_id(TDX_OPERAND_INVALID, OPERAND_ID_RDX);

goto EXIT;

}

[...]

for(uint64_t i = 0; i < num_of_tdmr_entries; i++)

{

...

update_pamt_array(tdmr_info_copy, pamt_data_array, (uint32_t)i);

// save tdmr's pamt data

}

tdx_global_data_ptr->num_of_tdmr_entries = (uint32_t)num_of_tdmr_entries;

```

A malicious VMM can exploit this issue by calling tdh\_sys\_config twice: The first call configures MAX\_TDMRS entries, but triggers an error on the last entry by specifying an overlapping or otherwise invalid TDMR. The second call configures X entries with X<MAX\_TDMR. tdmr\_table[0..X-1] and tdmr\_table[X..MAX\_TDMR-1] can now contain overlapping TDMRs.

As tdh\_sys\_tdmr\_init doesn't correctly limit the iteration count to X, an attacker can use this to create overlapping PAMT entries breaking one of the fundamental assumptions of the codebase.

While this bug did exist in the TDX module version shared with us during the review, it was already known to Intel. The fixed version correctly limits the loop to

```

tdx_global_data_ptr->num_of_tdmr_entries

```

Incorrect error handling in tdh\_mng\_rd\_wr

The TDH.MNG.RD/WR API calls can be used to read and write control structure fields of debuggable TDs.

```

Both variants are implemented in the function tdh_mng_rd_wr in src/vmm_dispatcher/api_calls/tdh_mng_rd_wr.c

```

At the beginning of the function, the code acquires a shared lock to the Trust Domain Root (TDR) of the target TD and maps its Trust Domain Control Structure (TDCS) into the virtual address space. To work correctly, all return paths from the function need to make sure that the lock is released and the page is unmapped.

In tdh\_mng\_rd\_wr this was implemented using a EXIT label at the end of the function and using "goto EXIT" instead of early returns for error handling. However, one of the error cases did perform an early return instead of a goto without releasing the lock and freeing the page mappings:

```

// Check that previous value has the expected value

if (prev_value != rd_value)

{

return api_error_with_operand_id(TDX_OPERAND_BUSY, OPERAND_ID_RDX);

}

```

The impact of vulnerabilities like this strongly depends on the underlying implementation locking and paging implementations. In the case of TDX module repeated triggering of this bug can lead to Use-After-Free issue as the Keyhole manager used for page mapping uses a 32bit integer for reference counting and the early return is missing a call to free\_la(tdr\_ptr).

Again, this bug was part of the initial shared codebase but already known to Intel. The issue was fixed by converting the early return into a goto. Additionally, we recommended hardening the keyhole manager against similar issues by either switching to a uint64\_t counter or adding checks to prevent over- and underflows.

#### Off-by-one in shared hpa check

Auditing the module's security checks for correctness was a high priority. We paid close attention to how it handles input in its boundary conditions. An important attack vector is the processing of shared memory addresses: the module sanitizes host address spaces, maps them to its virtual address space, and reads/writes to these locations.

Most security checks on a shared Host Physical Address (HPA) value take place in the function shared\_hpa\_check:

```

api_error_code_e shared_hpa_check(pa_t hpa, uint64_t size)

{

// 1) Check that no bits above MAX_PA are set

if (!is_pa_smaller_than_max_pa(hpa.raw))

{

return TDX_OPERAND_INVALID;

}

// 2) Check that the provided HPA is outside SEAMRR.

uint64_t seamrr_base = get_global_data()->seamrr_base;

uint64_t seamrr_size = get_global_data()->seamrr_size;

if (!is_valid_integer_range(seamrr_base, seamrr_size) ||

!is_valid_integer_range(get_addr_from_pa(hpa), TDX_PAGE_SIZE_IN_BYTES) ||

is_overlap(get_addr_from_pa(hpa), size, seamrr_base, seamrr_size))

{

}

```

```

return TDX_OPERAND_INVALID;

}

// 3) Check that HKID bits in the HPA are in the range configured for shared

HKIDs (0 to MAX_MKTME_HKIDS - 1).

if ((uint64_t)get_hkid_from_pa(hpa) > get_global_data()->max_mktme_hkids)

{

return TDX_OPERAND_INVALID;

}

return TDX_SUCCESS;

}

```

Note the boundary conditions in check #3: the module accepts HKIDs in [0, max\_mktme\_hkids] inclusive. The max value is initialized as follows:

```

tdx_global_data_ptr->max_mktme_hkids = MIN(

tdx_global_data_ptr->plt_common_config.ia32_tme_capability.mk_tme_max_keys,

BIT(tdx_global_data_ptr->plt_common_config.ia32_tme_activate.mk_tme_keyid_bits -

tdx_global_data_ptr->plt_common_config.ia32_tme_activate.tdx_reserved_keyid_bits)

- 1);

```

A typo in one of the MIN sub-expressions (the "-1" subtraction should be outside the MIN expression) inadvertently computes the wrong max value, which could, if triggered, be used to bypass shared\_hpa\_check.